CS61583 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS61583 Datasheet PDF : 44 Pages

| |||

CS61583

ter will output a maximum of 50 mA-rms, as re-

quired by European specification BS6450.

RECEIVER

The receiver extracts data and clock from the

T1/E1 signal on the line interface and outputs

clock and synchronized data to the system. The

signal is detected differentially across the receive

transformer and can be recovered over the entire

range of short haul cable lengths. The transmit

and receive transfomer specifications are identical

and are presented in the Applications section.

As shown in Table 1, the receiver slicing level is

set at 65% for DS1/DSX-1 short-haul and at

50% for all other applications.

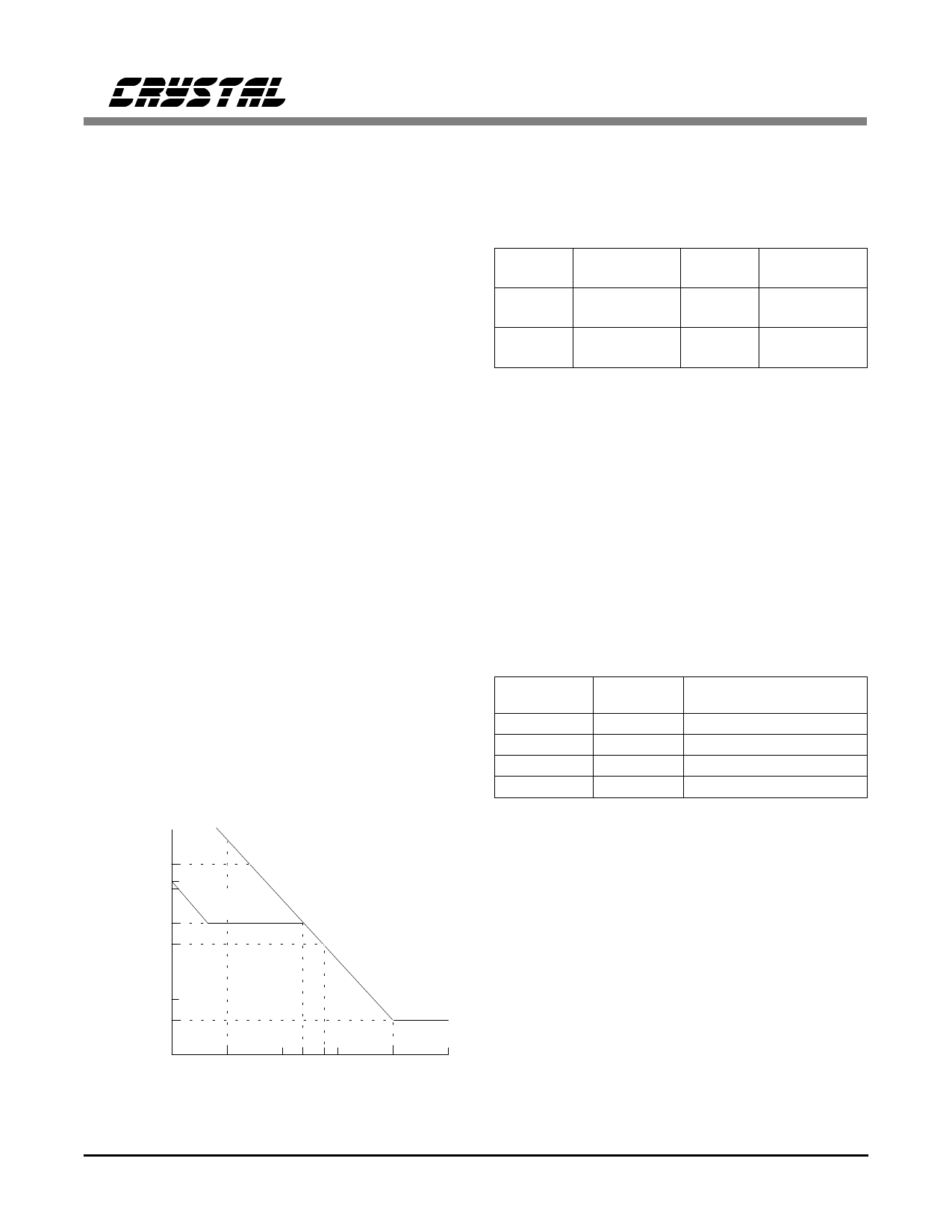

The clock recovery circuit is a second-order

phase locked loop that can tolerate up to 0.4 UI

of jitter from 10 kHz to 100 kHz without gener-

ating errors (Figure 8). The clock and data

recovery circuit is tolerant of long strings of con-

secutive zeros and will successfully recover a

1-in-175 jitter-free line input signal.

Recovered data at RPOS and RNEG (or

RDATA) is stable and may be sampled using the

recovered clock RCLK. The CLKE input deter-

mines the clock polarity for which output data is

stable and valid as shown in Table 2. When

300

138

100

28

PEAK-TO-PEAK

JITTER

10

(unit intervals)

CS61583

Performance

AT&T 62411

(1990 Version)

1

.4

.1

1

10

100 300 700 1k

10k

100k

JITTER FREQUENCY (Hz)

Figure 8. Minimum Input Jitter Tolerance of Receiver

(Clock Recovery Circuit and Jitter Attenuator)

12

CLKE is low, RPOS and RNEG (or RDATA) are

valid on the rising edge of RCLK. When CLKE

is high, RPOS and RNEG (or RDATA) are valid

on the falling edge of RCLK.

CLKE

LOW

HIGH

DATA

RPOS, RNEG

or RDATA

RPOS, RNEG

or RDATA

CLOCK

RCLK

RCLK

RCLK

RCLK

Clock Edge

for Valid Data

Rising

Rising

Falling

Falling

Table 2. Recovered Data/Clock Options

JITTER ATTENUATOR

The jitter attenuator can be switched into either

the receive or transmit paths. Alternatively, it can

also be removed from both paths to reduce the

propagation delay.

The location of the attenuators for both channels

is controlled by the ATTEN0 and ATTEN1 pins.

Table 3 shows how these pins are decoded.

ATTEN1

0

0

1

1

ATTEN0

0

1

0

1

Location of

Jitter Attenuator

Receiver

Disabled

Transmitter

Reserved

Table 3. Jitter Attenuation Control

The attenuator consists of a 64-bit FIFO, a nar-

row-band monolithic PLL, and control logic.

Signal jitter is absorbed in the FIFO which is de-

signed to neither overflow nor underflow. If

overflow or underflow is imminent, the jitter

transfer function is altered to insure that no bit-

errors occur. Under this condition, jitter gain

may occur and jitter should be attenuated exter-

nally in a frame buffer. The jitter attenuator will

typically tolerate 43 UIs before the overflow/un-

derflow mechanism occurs. If the jitter

attenuator has not had time to "lock" to the aver-

DS172PP5