CS61304A データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS61304A Datasheet PDF : 32 Pages

| |||

CS61304A

CS61304A

MODE

(pin 5)

CLKE

(pin 28)

LOW

X

(<0.2V)

HIGH

LOW

(>(V+) - 0.2V)

HIGH

HIGH

(>(V+) - 0.2V)

MIDDLE

X

(2.5V)

X = Don’t care

DATA

RPOS

RNEG

RPOS

RNEG

SDO

RPOS

RNEG

SDO

RDATA

CLOCK Clock Edge

for Valid Data

RCLK

RCLK

Rising

Rising

RCLK

RCLK

SCLK

Rising

Rising

Falling

RCLK

RCLK

SCLK

Falling

Falling

Rising

RCLK

Falling

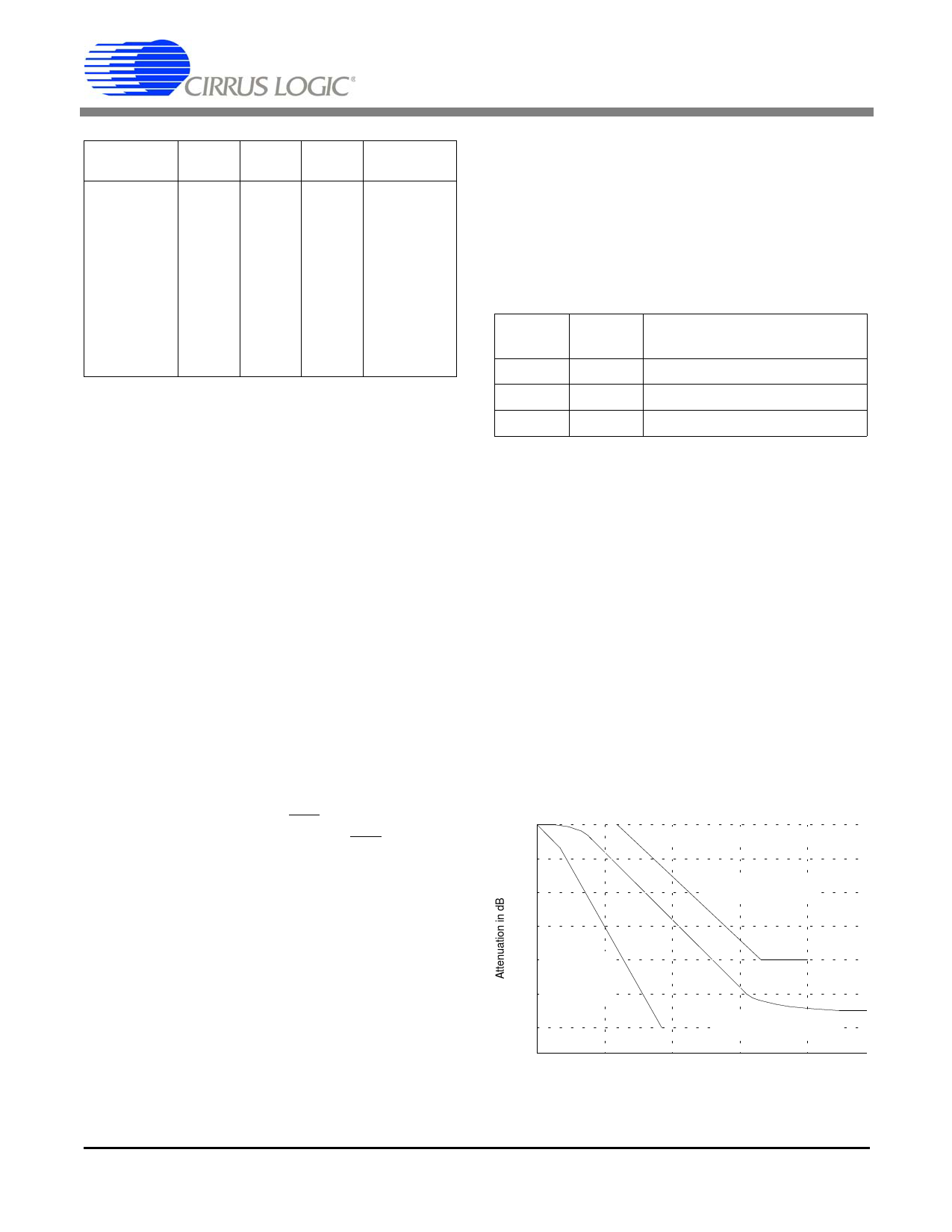

Table 5. Data Output/Clock Relationship

Loss of Signal

The receiver will indicate loss of signal after

power-up, reset or upon receiving 175 consecu-

tive zeros. A digital counter counts received

zeros, based on RCLK cycles. A zero is received

when the RTIP and RRING inputs are below the

input comparator slicing threshold level estab-

lished by the peak detector. After the signal is

removed for a period of time the data slicing

threshold level decays to approximately

300 mVpeak.

The receiver reports loss of signal by setting the

Loss of Signal pin, LOS, high. If the serial inter-

face is used, the LOS bit will be set and an

interrupt will be issued on INT (unless disabled).

LOS will return low (asserting the INT pin again

in Host Mode) upon receipt of 3 ones in 32 bit

periods with no more than 15 consecutive zeros.

Note that in the Host Mode, LOS is simultane-

ously available from both the register and pin 12.

RPOS/RNEG or RDATA are forced low during

LOS unless the jitter attenuator is disabled. (See

"Jitter Attenuator")

If ACLKI is present during the LOS state, ACLKI

is switched into the input of the jitter attenuator,

resulting in RCLK matching the frequency of

ACLKI. The jitter attenuator buffers any instanta-

neous changes in phase between the last

DS156PFP1 2

recovered clock and the ACLKI reference clock.

This means that RCLK will smoothly transition

to the new frequency. If ACLKI is not present,

then the crystal oscillator of the jitter attenuator is

forced to its center frequency. Table 6 shows the

status of RCLK upon LOS.

Crystal ACLKI

present? present?

Source of RCLK

No

Yes

ACLKI

Yes

No

Centered Crystal

Yes

Yes ACLKI via the Jitter Attenuator

Table 6. RCLK Status at LOS

Jitter Attenuator

The jitter attenuator reduces wander and jitter in

the recovered clock signal. It consists of a FIFO,

a crystal oscillator, a set of load capacitors for the

crystal, and control logic. The jitter attenuator ex-

ceeds the jitter attenuation requirements of

Publications 43802 and REC. G.742. A typical

jitter attenuation curve is shown in Figure 12. The

CS61304A fully meets AT&T 62411 jitter attenu-

ation requirements.

0

a) Minimum Attenuation Limit

10

20

62411 Requirements

30

40 b) Maximum

Attunuation

50

Limit

60

Measured Performance

1

10

100

1k

10 k

Frequency in Hz

Figure 12. Typical Jitter Transfer Function

1133