CS61304A データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS61304A Datasheet PDF : 32 Pages

| |||

CS61304A

CS61304A

The jitter attenuator works in the following man-

ner. The recovered clock and data are input to the

FIFO with the recovered clock controlling the

FIFO’s write pointer. The crystal oscillator con-

trols the FIFO’s read pointer which reads data out

of the FIFO and presents it at RPOS and RNEG

(or RDATA). The update rate of the read pointer

is analogous to RCLK. By changing the load ca-

pacitance that the IC presents to the crystal, the

oscillation frequency is adjusted to the average

frequency of the recovered signal. Logic deter-

mines the phase relationship between the read and

write pointers and decides how to adjust the load

capacitance of the crystal. Jitter is absorbed in the

FIFO.

The FIFO in the jitter attenuator is designed to

prevent overflow and underflow. If the jitter am-

plitude becomes very large, the read and write

pointers may get very close together. Should they

attempt to cross, the oscillator’s divide by four

circuit adjusts by performing a divide by 3 1/2 or

divide by 4 1/2 to prevent data loss from overflow

or underflow.

The jitter attenuator may be bypassed by pulling

XTALIN to RV+ through a 1 kΩ resistor and pro-

viding a 1.544 MHz (or 2.048 MHz) clock on

ACLKI. RCLK may exhibit quantization jitter of

approximately 1/13 UIpp and a duty cycle of ap-

proximately 30% (70%) when the attenuator is

disabled.

Local Loopback

Local loopback is selected by taking LLOOP, pin

27, high or by setting the LLOOP register bit via

the serial interface.

The local loopback mode takes clock and data

presented on TCLK, TPOS, and TNEG (or

TDATA), sends it through the jitter attenuator and

outputs it at RCLK, RPOS and RNEG (or

RDATA). If the jitter attenuator is disabled, it is

bypassed. Inputs to the transmitter are still trans-

mitted on TTIP and TRING, unless TAOS has

been selected in which case, AMI-coded continu-

ous ones are transmitted at the TCLK frequency.

The receiver RTIP and RRING inputs are ignored

when local loopback is in effect.

Remote Loopback

Remote loopback is selected by taking RLOOP,

pin 26, high or by setting the RLOOP register bit

via the serial interface.

In remote loopback, the recovered clock and data

input on RTIP and RRING are sent through the

jitter attenuator and back out on the line via TTIP

and TRING. Selecting remote loopback overrides

any TAOS request (see Table 7). The recovered

incoming signals are also sent to RCLK, RPOS

and RNEG (or RDATA). A remote loopback oc-

curs in response to RLOOP going high.

Simultaneous selection of local and remote loop-

back modes is not valid (see Reset).

In the Extended Hardware Mode the transmitted

data is looped before the AMI/B8ZS/HDB3 en-

coder/decoder during remote loopback so that the

transmitted signal matches the received signal,

even in the presence of received bipolar viola-

tions. Data output on RDATA is decoded,

however, if RCODE is low.

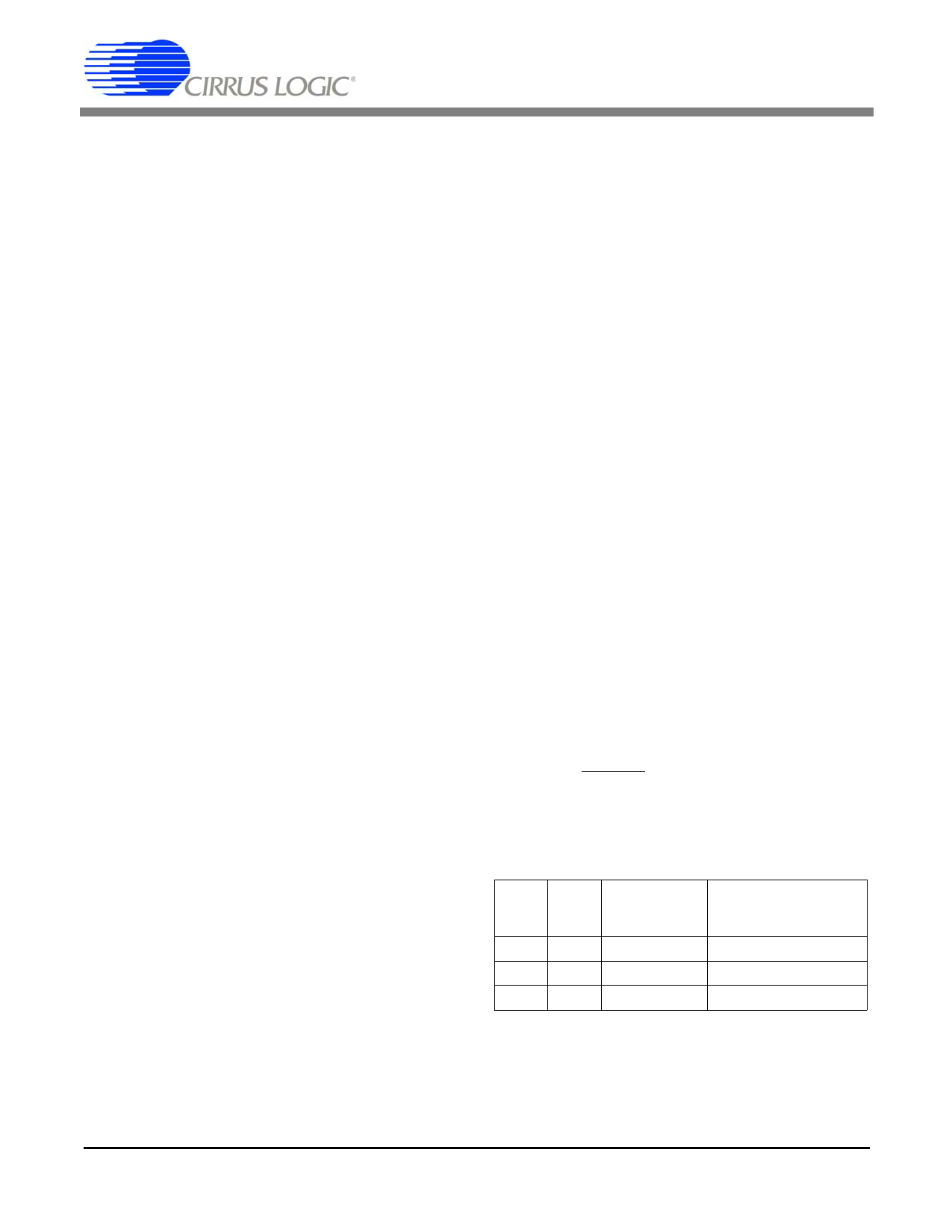

RLOOP TAOS Source of

Input Input

Data for

Signal Signal TTIP & TRING

Source of

Clock for

TTIP & TRING

0

0

TDATA

TCLK

0

1

all 1s

TCLK

1

X RTIP & RRING RTIP & RRING (RCLK)

Notes: 1. X = Don’t Care. The identified All Ones Select

input is ignored when the indicated loopback is

in effect.

2. Logic 1 indicates that Loopback or All Ones

option is selected.

Table 7. Interaction of RLOOP with TAOS

14

DSD1S5165P6PF21