CS61304A データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS61304A Datasheet PDF : 32 Pages

| |||

CS61304A

CS61304A

Driver Performance Monitor

To aid in early detection and easy isolation of

non-functioning links, the IC is able to monitor

transmit drive performance and report when the

driver is no longer operational. This feature can

be used to monitor either the device’s perform-

ance or the performance of a neighboring driver.

The driver performance monitor indicator is nor-

mally low, and goes high upon detecting a driver

failure.

The driver performance monitor consists of an ac-

tivity detector that monitors the transmitted signal

when MTIP is connected to TTIP and MRING is

connected to TRING. DPM will go high if the

absolute difference between MTIP and MRING

does not transition above or below a threshold

level within a time-out period. In the Host Mode,

DPM is available from both the register and pin

11.

Whenever more than one line interface IC resides

on the same circuit board, the effectiveness of the

driver performance monitor can be maximized by

having each IC monitor performance of a neigh-

boring IC, rather than having it monitor its own

performance.

Alarm Indication Signal

In the Extended Hardware Mode, the receiver sets

the output pin AIS high when less than 3 zeros

are detected out of 2048 bit periods. AIS returns

low when 4 or more zeros, out of 2048 bits, are

detected.

Line Code Encoder/Decoder

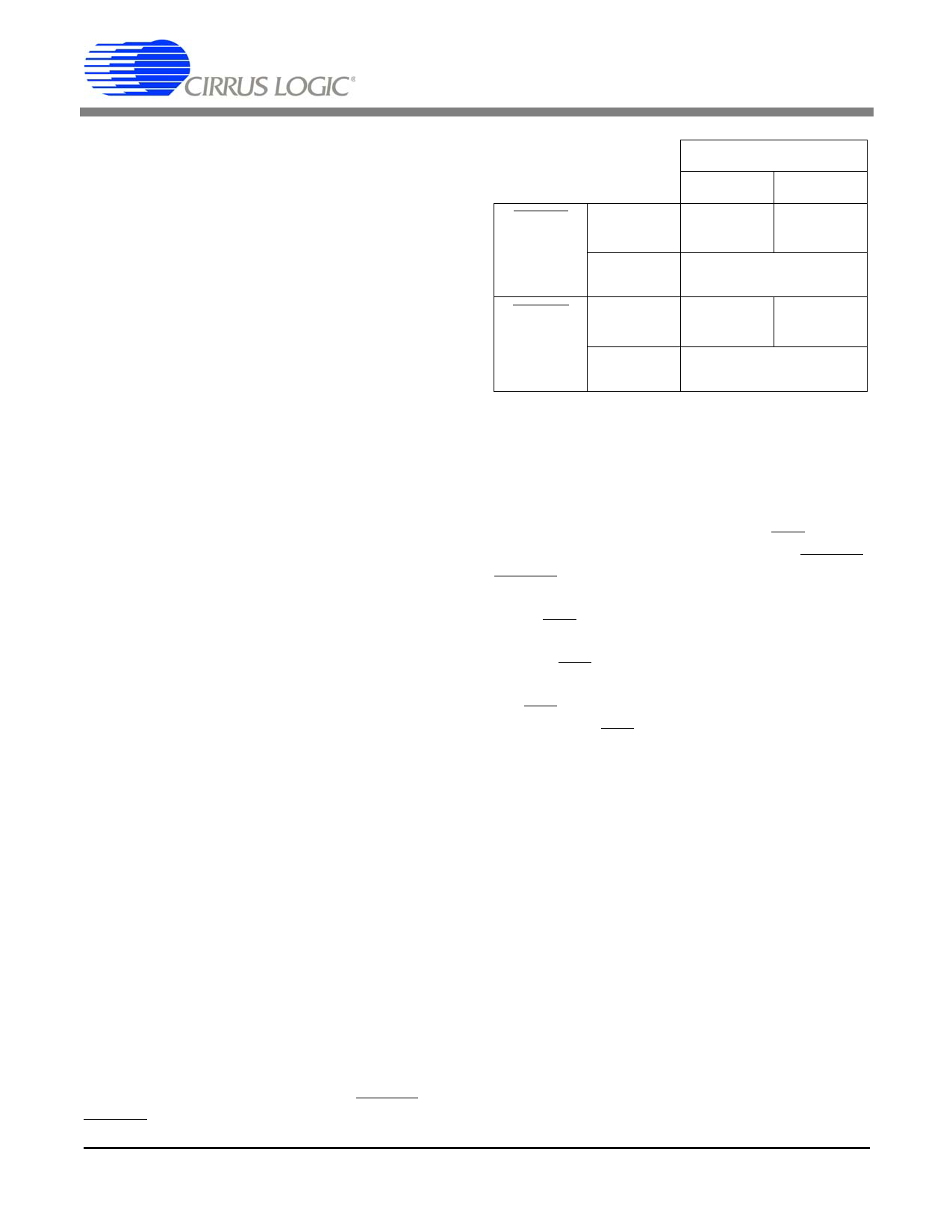

In the Extended Hardware Mode, three line codes

are available: AMI, B8ZS and HDB3. The input

to the encoder is TDATA. The outputs from the

decoder are RDATA and BPV (Bipolar Violation

Strobe). The encoder and decoder are selected

using the LEN2, LEN1, LEN0, TCODE and

RCODE pins as shown in Table 8.

DS156PFP1 2

TCODE

(Transmit

Encoder

Selection)

RCODE

(Receiver

Decoder

Selection)

LOW

HIGH

LOW

HIGH

LEN 2/1/0

000

010-111

HDB3

Encoder

B8ZS

Encoder

AMI Encoder

HDB3

Decoder

B8ZS

Decoder

AMI Decoder

Table 8. Encoder/Decoder Selection

Parallel Chip Select

In the Extended Hardware Mode, PCS can be

used to gate the digital control inputs: TCODE,

RCODE, LEN0, LEN1, LEN2, RLOOP, LLOOP

and TAOS. Inputs are accepted on these pins only

when PCS is low and will immediately change

the operating state of the device. Therefore, when

cycling PCS to update the operating state, the

digital control inputs should be stable for the en-

tire PCS low period. The digital control inputs are

ignored when PCS is high.

Power On Reset / Reset

Upon power-up, the IC is held in a static state

until the supply crosses a threshold of approxi-

mately 3 Volts. When this threshold is crossed,

the device will delay for about 10 ms to allow the

power supply to reach operating voltage. After

this delay, calibration of the delay lines used in

the transmit and receive sections commences. The

delay lines can be calibrated only if a reference

clock is present. The reference clock for the re-

ceiver is provided by the crystal oscillator, or

ACLKI if the oscillator is disabled. The reference

clock for the transmitter is provided by TCLK.

The initial calibration should take less than

20 ms.

1155