5962F9563501QXC データシートの表示(PDF) - Intersil

部品番号

コンポーネント説明

メーカー

5962F9563501QXC Datasheet PDF : 36 Pages

| |||

HS-RTX2010RH

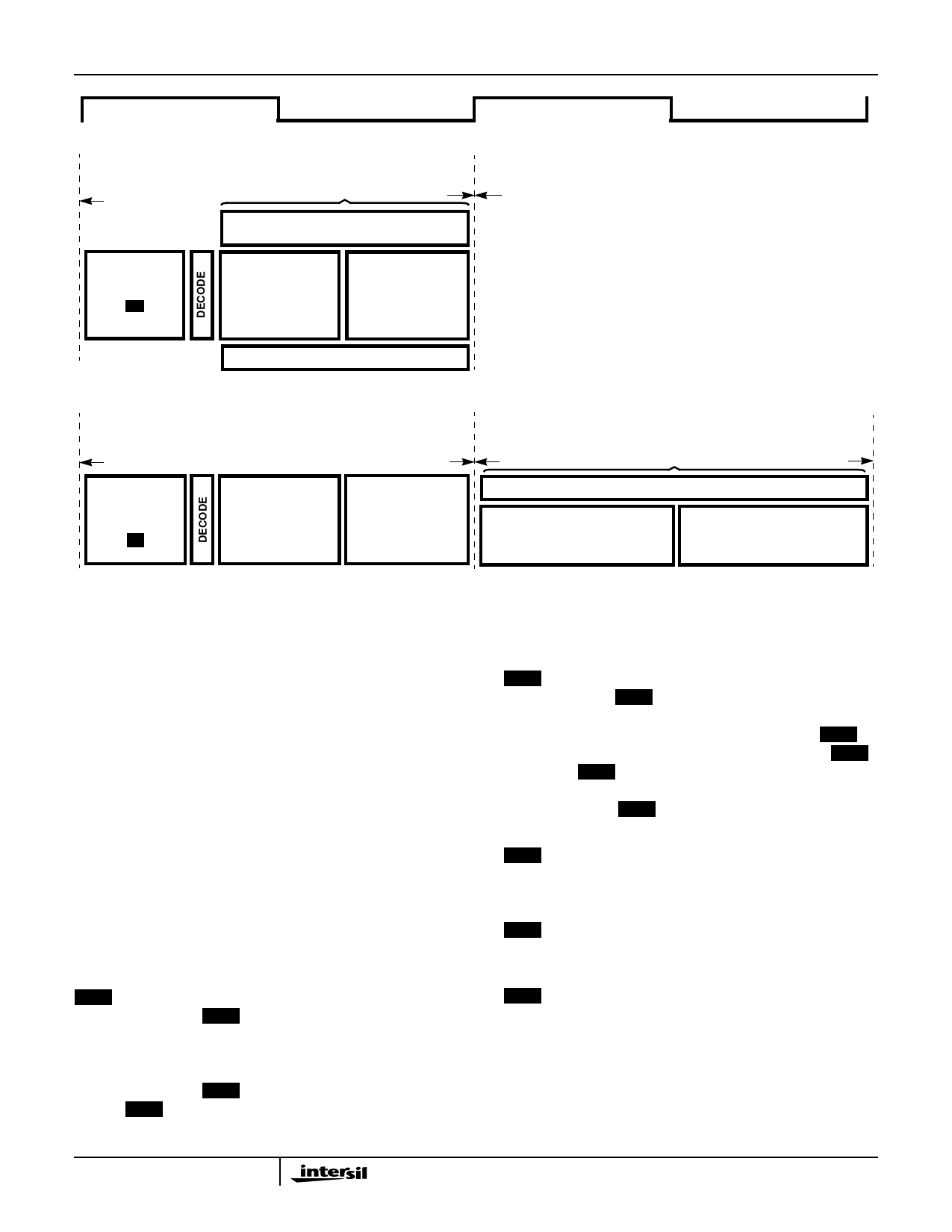

PCLK

EXECUTION SEQUENCE WITH NO MEMORY DATA ACCESS:

BEGIN

FIRST

CLOCK

CYCLE

CONCURRENT

OPERATIONS

END OF

FIRST

CLOCK

CYCLE

BEGIN

SECOND

CLOCK

CYCLE

INSTRUCTION

LATCHES INTO

IR

PERFORM INTERNAL OPERATIONS AND

ALU OPERATIONS, AS REQUIRED

ADDRESS OF

NEXT

INSTRUCTION

IS PLACED ONTO

MA19-MA01

BUS

FETCH

ASIC BUS OPERATIONS

EXECUTION SEQUENCE WITH MEMORY DATA ACCESS:

BEGIN

FIRST

CLOCK

CYCLE

END OF

FIRST

CLOCK

CYCLE

BEGIN

SECOND

CLOCK

CYCLE

CONCURRENT

OPERATIONS

END OF

SECOND

CLOCK

CYCLE

INSTRUCTION

LATCHES

INTO

IR

ADDRESS OF

MEMORY

LOCATION

IS PLACED ONTO

MA19-MA01

BUS

READ OR WRITE

MEMORY DATA

PERFORM ALU OPERATIONS

PLACE ADDRESS OF

NEXT INSTRUCTION

ONTO MA19-MA01

FETCH NEXT

INSTRUCTION

FIGURE 10. INSTRUCTION EXECUTION SEQUENCE

RTX Data Buses and Address Buses

The RTX core bus architecture provides for unidirectional

data paths and simultaneous operation of some data buses.

This parallelism allows for maximum efficiency of data flow

internal to the core.

Addresses for accessing external (off-chip) memory or

ASIC devices are output via either the Memory Data Bus

(MA19-MA01) or the ASIC Address Bus (GA02-GA00). See

Table 3. External data is transferred by the ASIC Data Bus

(GD15-GD00) and the Memory Data Bus (MD15-MD00),

both of which are bidirectional.

RTX Internal Registers

The core of the HS-RTX2010RH is a macrocell available

through the Intersil Standard Cell Library. This core contains

eight 16-bit internal registers, which may be accessed

implicitly or explicitly, depending upon the register accessed

and the function being performed.

TOP : The Top Register contains the top element of the

Parameter Stack++. TOP is the implicit data source or

destination for certain instructions, and has no ASIC address

assignment. The contents of this register may be directed to

any I/O device or to any processor register except the

Instruction Register. TOP is also the T input to the ALU.

Input to TOP must come through the ALU. This register

also holds the most significant 16 bits of 32-bit products and

32-bit dividends.

NEXT: The Next Register holds the second element of the

Parameter Stack. EXT is the implicit data source or

destination for certain instructions, and has no ASIC address

assignment. During a stack “push”, the contents of NEXT

are transferred to stack memory, and the contents of TOP

are put into NEXT. This register is used to hold the least

significant 16 bits of 32-bit products. Memory data is

accessed through NEXT, as described in the Memory

Access section of this document.

IR : The Instruction Register is actually a latch which

contains the instruction currently being executed, and has no

ASIC address assignment. In certain instructions, an

operand can be embedded in the instruction code, making

IR the implicit source for that operand (as in the case of

short literals). Input to this register comes from Main

Memory (see Tables 6 thru 22 for code information).

CR : The Configuration Register is used to indicate and

control the current status/setup of the RTX microcontroller,

through the bit assignments shown in Figure 11. This

register is accessed explicitly through read and write

operations, which cause interrupts to be suppressed for one

cycle, guaranteeing that the next instruction will be

performed before an Interrupt Acknowledge cycle is allowed

to be performed.

11