M80C286 データシートの表示(PDF) - Intel

部品番号

コンポーネント説明

メーカー

M80C286 Datasheet PDF : 60 Pages

| |||

M80C286

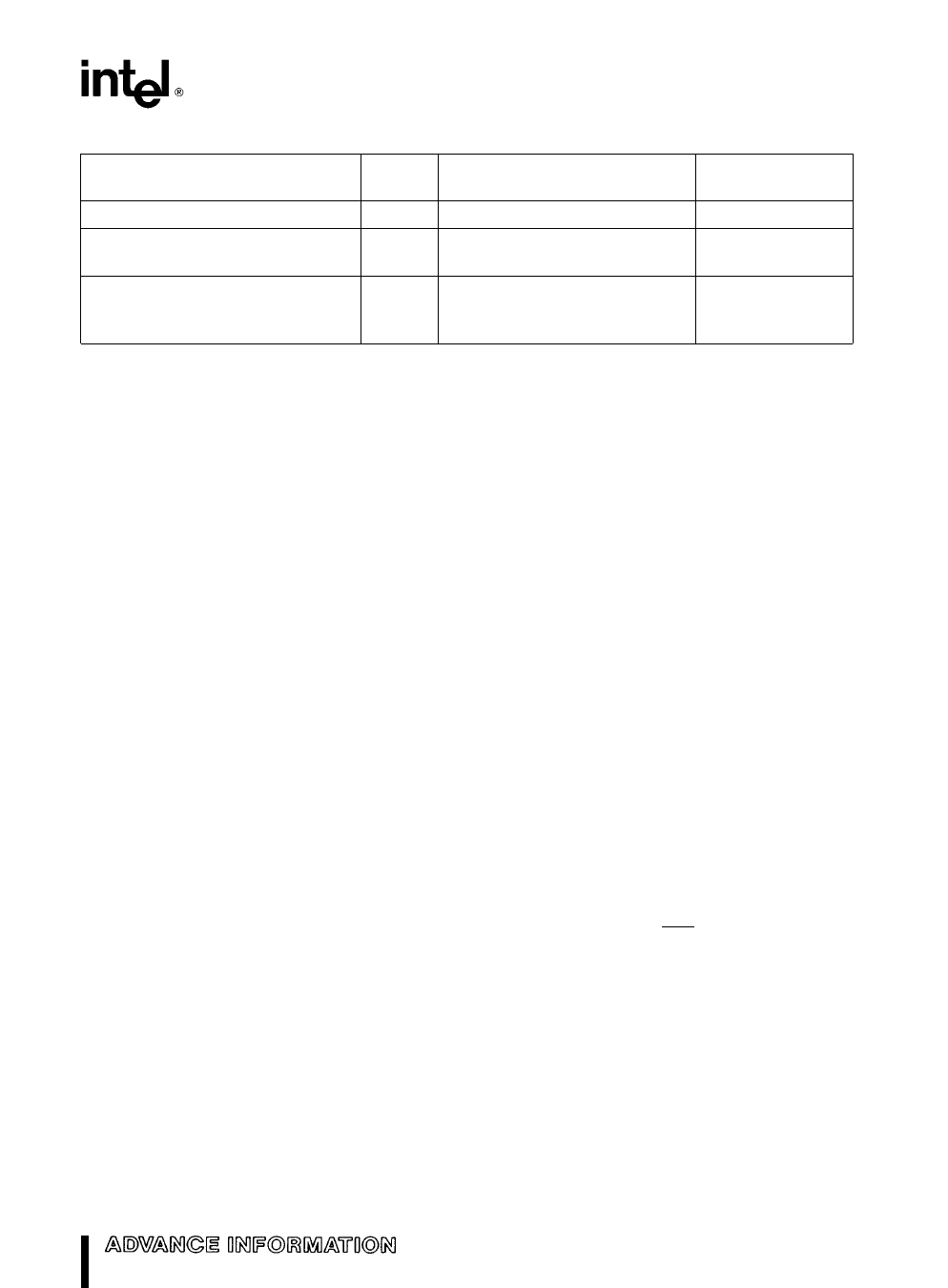

Table 9 Real Address Mode Addressing Interrupts

Function

Interrupt

Number

Related

Instructions

Return Address

Before Instruction

Interrupt table limit too small exception 8 INT vector is not within table limit

Yes

Processor extension segment overrun

9 ESC with memory operand extend-

No

interrupt

ing beyond offset FFFF(H)

Segment overrun exception

13 Word memory reference with offset

Yes

e FFFF(H) or an attempt to exe-

cute past the end of a segment

Interrupts

Table 9 shows the interrupt vectors reserved for ex-

ceptions and interrupts which indicate an addressing

error The exceptions leave the CPU in the state ex-

isting before attempting to execute the failing in-

struction (except for PUSH POP PUSHA or POPA)

Refer to the next section on protected mode initiali-

zation for a discussion on exception 8

Protected Mode Initialization

To prepare the M80C286 for protected mode the

LIDT instruction is used to load the 24-bit interrupt

table base and 16-bit limit for the protected mode

interrupt table This instruction can also set a base

and limit for the interrupt vector table in real address

mode After reset the interrupt table base is initial-

ized to 000000(H) and its size set to 03FF(H) These

values are compatible with M8086 88 software

LIDT should only be executed in preparation for pro-

tected mode

Shutdown

Shutdown occurs when a severe error is detected

that prevents further instruction processing by the

CPU Shutdown and halt are externally signalled via

a halt bus operation They can be distinguished by

A1 HIGH for halt and A1 LOW for shutdown In real

address mode shutdown can occur under two con-

ditions

Exceptions 8 or 13 happen and the IDT limit does

not include the interrupt vector

A CALL INT or PUSH instruction attempts to wrap

around the stack segment when SP is not even

An NMI input can bring the CPU out of shutdown if

the IDT limit is at least 000F(H) and SP is greater

than 0005(H) otherwise shutdown can only be exit-

ed via the RESET input

PROTECTED VIRTUAL ADDRESS

MODE

The M80C286 executes a fully upward-compatible

superset of the M8086 instruction set in protected

virtual address mode (protected mode) Protected

mode also provides memory management and pro-

tection mechanisms and associated instructions

The M80C286 enters protected virtual address

mode from real address mode by setting the PE

(Protection Enable) bit of the machine status word

with the Load Machine Status Word (LMSW) instruc-

tion Protected mode offers extended physical and

virtual memory address space memory protection

mechanisms and new operations to support operat-

ing systems and virtual memory

All registers instructions and addressing modes de-

scribed in the M80C286 Base Architecture section

of this Functional Description remain the same Pro-

grams for the M8086 88 186 and real address

mode M80C286 can be run in protected mode how-

ever embedded constants for segment selectors

are different

Memory Size

The protected mode M80C286 provides a 1 gigabyte

virtual address space per task mapped into a 16

megabyte physical address space defined by the ad-

dress pin A23–A0 and BHE The virtual address

space may be larger than the physical address

space since any use of an address that does not

map to a physical memory location will cause a re-

startable exception

Memory Addressing

As in real address mode protected mode uses 32-

bit pointers consisting of 16-bit selector and offset

components The selector however specifies an in-

dex into a memory resident table rather than the up-

per 16-bits of a real memory address The 24-bit

base address of the desired segment is obtained

11